FREE SHIPPING ON ALL BUSHNELL PRODUCTS

EPM570T100I5N IC CPLD 440MC 5.4NS 100TQFP

פרמטר מוצר

תיאור

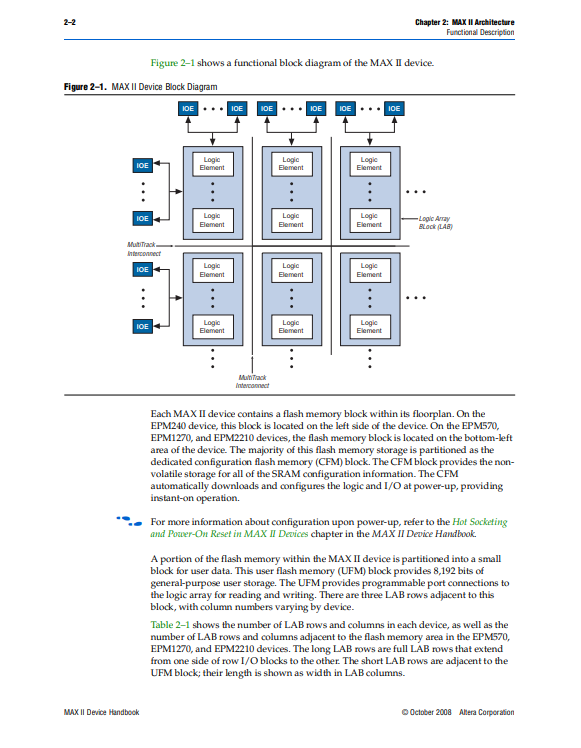

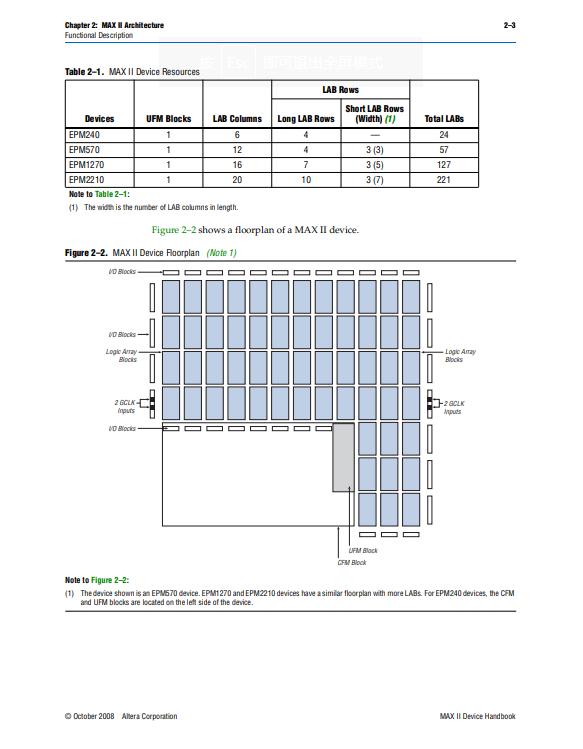

משפחת MAX® II של רכיבי CPLD מיידיים ובלתי נדיפים מבוססת על תהליך הבזק של 0.18 מיקרומטר, 6-שכבות-מתכת, עם צפיפויות של 240 עד 2,210 אלמנטים לוגיים (LEs) (128 עד 2,210 תאים מקבילים) ו אחסון לא נדיף של 8 Kbits.התקני MAX II מציעים ספירת קלט/פלט גבוהה, ביצועים מהירים והתאמה אמינה לעומת ארכיטקטורות CPLD אחרות.עם ליבת MultiVolt, בלוק זיכרון הבזק למשתמש (UFM) ויכולת תכנות משופרת בתוך המערכת (ISP), התקני MAX II מתוכננים להפחית עלויות והספק תוך מתן פתרונות ניתנים לתכנות עבור יישומים כגון גישור אפיק, הרחבת קלט/פלט, חשמל -ב איפוס (POR) ובקרת רצף, ובקרת תצורת המכשיר.

| מפרטים: | |

| תְכוּנָה | ערך |

| קטגוריה | מעגלים משולבים (ICs) |

| Embedded - CPLDs (התקני לוגיקה מורכבים לתכנות) | |

| מר | אינטל |

| סִדרָה | MAX® II |

| חֲבִילָה | מַגָשׁ |

| סטטוס חלק | פָּעִיל |

| סוג ניתן לתכנות | בתכנות מערכת |

| זמן השהיה tpd(1) מקסימום | 5.4 ns |

| אספקת מתח - פנימית | 2.5V, 3.3V |

| מספר אלמנטים/בלוקים לוגיים | 570 |

| מספר Macrocells | 440 |

| מספר קלט/פלט | 76 |

| טמפרטורת פעולה | -40°C ~ 100°C (TJ) |

| סוג הרכבה | מתקן משטח |

| חבילה / מארז | 100-TQFP |

| חבילת מכשירי ספק | 100-TQFP (14x14) |

| מספר מוצר בסיס | EPM570 |

כתבו כאן את הודעתכם ושלחו אותה אלינו

קָשׁוּרמוצרים

-

טל

-

אימייל

-

סקייפ

-

ווטסאפ

ווטסאפ